組み込みシステム

eXCite

C言語ハードウェア設計ツールFPGA&ASICソリューション

- C言語高位合成エンジンと通信合成エンジンをパッケージ化

- ASIC/FPGA設計に対応

製品概要

ISO/ANSI-Cから簡単にハードウェアを作るためのC言語高位合成エンジンと通信合成エンジンの基本部分をパッケージ化した製品です。eXCiteには、ASIC/FPGA設計に対応した「eXCite Professional」とFPGA設計に特化した「eXCite FPGA」があります。

eXCite Professional 版

eXCite が装備しているC言語高位合成の優れた機能の全てが搭載された製品です。ASIC設計にも利用可能です。

サポートプラットフォーム: Windows、Linux

ライセンス形態: フローティング、ノードロック (永久ライセンス、タームライセンス有)

eXCite Standard 版

eXCite が装備しているC言語高位合成の基本機能を削ることなく、ターゲットデバイスをFPGAに限定、またプラットフォームをWindows環境に限定することで、ASIC 開発用に特化されている機能の一部を削減し、コストダウンを実現した製品です。

サポートプラットフォーム: Windows

ライセンス形態: ノードロック(永久ライセンス、タームライセンス有)

eXCite Altera(Intel) 版

ターゲットデバイスをアルテラ社 FPGA に限定、またプラットフォームをWindows環境に限定することで、Standard 版よりコストダウンを実現した製品です。

サポートプラットフォーム: Windows

ライセンス形態: ノードロック(タームライセンスのみ)

特長・機能

eXCiteの特長と機能

- GUI環境

- GUIは、誰にでも分かり易く、使い易いルックアンドフィールに仕上がっています。ユーザーは、合成用にC言語を用意し、ツール上のボタンを押すだけで、RTL HDLを生成できます。

- 高位合成エンジン

- C言語からRTL HDLを作るために、スケジューリング機能を搭載しています。HWとして最適な動作を設計制約(クロック周波数、コンポーネント数、インターフェイス)に応じて、最適なスケジューリングを自動で行い、RTL HDL(VHDL、Verilog)を出力します。

- 通信合成エンジン

- レジスタ、メモリ、FIFO、簡易バス、ワイヤ、他など様々なインターフェイスを、必要に応じて入力Cソースに付加できます。また、Altera社Avalonインタフェースにも対応そており、Qsys ToolやSOPC Builderで簡単にFPGAおよびFPGAボード全体を設計することができます。

- VHDL、Verilog出力

- 出力するRTL HDLは、VHDL, Verilogの両言語に対応しています。

- テスト環境

- 合成後のHDLを容易に検証するためのテスト環境構築支援ユーティリティツールを提供します。合成前に使用していたC環境とリンクした検証や、FPGAボードを利用した検証などが可能です。

- 論理合成可能なライブラリ

- 合成後のモデルを市販の論理合成ツールでそのまま合成できるように、論理合成可能なライブラリも付属しています。

- HWアーキテクチャ探索支援

- 合成制約を変更することで様々なHWアーキテクチャを検討できます。一つのCアルゴリズムから多くのHWアーキテクチャを検討し、生成することが可能です。

- パイプライン合成

- Loop文やモデル全体をパイプライン合成することが可能です。さらに、レイテンシやスループットをコード全体やLoop文に対して設定できます。

- ビットサイズ最適化

- C言語では、char->8bit, short->16bit, long->32bit のようにビット間隔のあるデータ型しか存在しませんが、eXCiteのビット最適化機能により、合成後のビットサイズを調整します。最適化オプションを有効にするだけで自動的に最適なビット幅を調整し、さらにユーザーが任意にビット幅を指定することも可能です。

- Loop文最適化

- Loop文を全展開、部分展開できます。これにより、並列性が大幅に向上します。

- Cコード最適化機能

- 無駄なオペレーションの削除や処理順番の入れ替え、乗算などを加算とシフト演算へ変換するなど多くのCコード最適化機能を搭載しています。この機能により、回路規模、処理スピードを大幅に改善します。

- 浮動小数点サポート

- float、doubleの浮動小数点演算をサポートします。

- アーキテクチャチューニング機能

- HW合成の際、コンポーネント割当を最適化(最大数割り当て及び共有化)する機能です。その結果、動作周波数を大きく上げ、さらに回路規模を縮小します。

- C言語階層化合成機能

- 関数の階層構造を保持した合成や、階層を平坦化する合成の選択が可能となり、多彩なアーキテクチャを表現できます。これにより、出力されたRTLの可読性や品質が向上します。さらに、既存のC言語アルゴリズムとのシステム再構築も可能ですので、設計資産を有効に活用します。

- 動作環境

- 対応OS: Windows、Linux

- ※ 但しeXCite FPGA は Windows のみ

Avalonインタフェースへ連携

eXCiteは、ALTERA(Intel)社Avalonインタフェース向けにAvalonプラットフォームライブラリを用意しています。設計者はCアルゴリズムから容易にAvalonインタフェースへ連結する高性能ハードウェアを合成し、ALTERA社のSOPC Builder、Quartus IIおよびNios IIを用いて実装できます。

仕様

| 入力言語 | ISO/ANSI-C |

| 出力言語 | RTL VHDL、Verilog(1995/2001) および SystemC |

| 対応OS | Windows、Linux ※ eXCite Standard/Altera は Windows のみ対応 |

| インストールHDD | 150MB 程度 |

| 推奨作業メモリ | 1GB以上 |

| 推奨CPU | Core i3 程度以上 |

| 必要コンパイラ | gcc (Linux版), Visual Studio(Windows版) |

| ライセンス | フローティングライセンス (eXCite Standard/Altera(Intel) はノードロックのみ) |

米国Y Explorations, Inc. (YXI)は、カリフォルニア州立大学アーバイン校での長年にわたる研究成果によって開発された、高位合成・通信合成・IP再利用の技術を中心に1995年に設立されたEDAベンダーです。 現在、ソリトンシステムズ関連会社として共同でeXCiteの開発およびC言語HW設計のソリューションを提供しております。

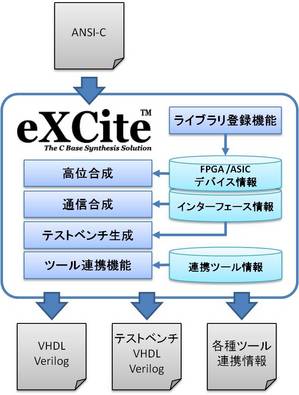

製品構成

C言語ハードウェア設計ツールeXCiteの機能

eXCiteは標準C言語からハードウェア設計者が普段記述するRTL HDL(VHDL、Verilog)を自動的に生成する設計環境です。動作しか記述されていないC言語からハードウェア記述を生成するために、eXCiteには、高位合成エンジン、通信合成エンジン、各種ライブラリをはじめ、出力結果の内容を検証するテストベンチ生成機能や下流工程にあるHDL検証ツールや論理合成ツールとの連動用環境構築の機能が備わっています。

価格についてはお問い合わせください。期間ライセンス、永久ライセンス(保守期間中のバージョンの永久使用権付ライセンス)をご用意しております。